This is article-5 of how to define Synthesis timing constraint

Logically exclusive clocks are active in the design but cannot interact with each other. When dealing with logically exclusive clock, one often sees a mux with the select line determining which clock is active. An important guideline to remember while dealing with logically exclusive clocks is that logically exclusive clocks shouldn’t interact outside the mux.

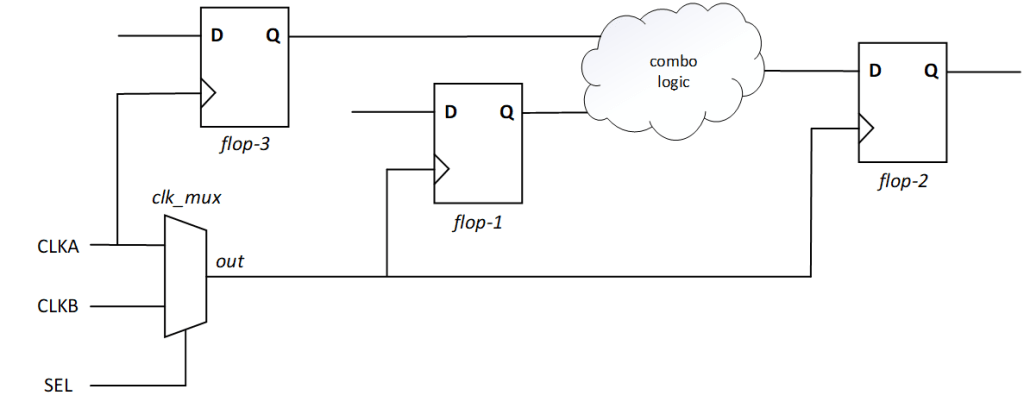

Consider the example shown in Figure 1, we have two clocks – CLKA and CLKB that are muxed, such that the design either operates either at CLKA or at CLKB. The user has the option to use a set_case_analysis constraint and apply a value of 0 or 1 to choose either between CLKA or CLKB; if this is done, then for timing analysis only the selected clock will be used by the synthesis tool. However if the select port is unconstrained, then both clocks are allowed to reach both the flip-flop’s clock pin, and either of the two clocks can be independently used as launch or capture clock edges, so the timing analysis will consider all the possible combination for worst case timing; in other words, muxed clocks are not inferred as exclusive clocks automatically for timing analysis. As a result, the synthesis optimization will consider all the following four cases –

| Launching clock in flop-1 | Capturing clock in flop-2 |

| CLKA | CLKA |

| CLKA | CLKB |

| CLKB | CLKA |

| CLKB | CLKB |

Of course, the two middle cases can never happen. So, to direct the synthesis tool to consider only CLKA → CLKA and CLKB → CLKB and to optimize the worst of those two cases only, we need to use –

set_clock_groups -logically_exclusive -group CLKA -group CLKB

By doing this the delay between the two registers will be optimized for the worst of CLKA → CLKA or CLKB → CLKB

Note: Alternatively, we can also apply two false paths for this case –

set_false_path -from [get_clocks CLKA] -to [get_clocks CLKB]

set_false_path -from [get_clocks CLKB] -to [get_clocks CLKA]

Consider the example shown in Figure 2, where the clocks interact outside the mux. If we use the constraint “set_clock_groups -logically_exclusive -group CLKA -group CLKB”, then the synthesis tool will consider only CLKA → CLKA and CLKB → CLKB will optimize the combination logic for the worst of those two cases only. But there is possibility that the data being launched in flop-3 at CLKA and being captured at flop-2 at CLKB is the worst-case scenario and therefore the combinational logic should be optimized accordingly.

Therefore, we need to create generated clocks for CLKA and CLKB, at the output of the mux –

create_generated_clock -name -CLKA_GEN -source CLKA [get_pins clk_mux/out]

create_generated_clock -name -CLKB_GEN -source CLKB [get_pins clk_mux/out]

Then only we need set the two generated clocks as logically exclusive –

set_clock_groups -logically_exclusive -group CLKA_GEN -group CLKB_GEN

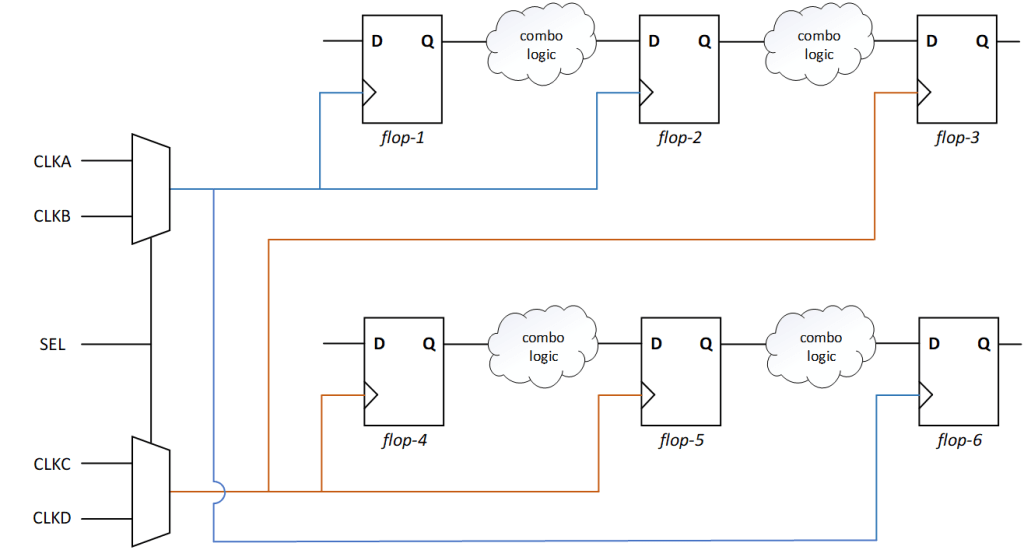

Consider the example shown in Figure 3, there are two pairs of clocks that are being independently muxed. CLKA and CLKB is controlled by SEL1 and CLKC and CLKD is controlled by SEL2. Notice that inside our design, the flops that are driven by CLKA or CLKB that communicate with flops being captured by CLKC or CLKD and vice-versa.

To constrain this design, we create two separate logically exclusive clock groups –

set_clock_groups -logically_exclusive -group CLKA -group CLKB

set_clock_groups -logically_exclusive -group CLKC -group CLKD

And the delay of each path will be optimized for the worst of the logically possible timing conditions.

Note: Alternatively, we can also apply four false paths for this case –

set_false_path -from [get_clocks CLKA] -to [get_clocks CLKB]

set_false_path -from [get_clocks CLKB] -to [get_clocks CLKA]

set_false_path -from [get_clocks CLKC] -to [get_clocks CLKD]

set_false_path -from [get_clocks CLKD] -to [get_clocks CLKC]

Consider the example shown in Figure 4, we have made one small change compared to the example shown in Figure 3; notice that the select line of the muxes, instead of being independent are now connected to each other.

Here we need to create a logically exclusive group between groups containing CLKA & CLKC and another containing CLKB & CLKD –

set_clock_groups -logically_exclusive -group “CLKA CLKC” -group “CLKB CLKD”

Clocks within the group can communicate with each other but clocks across groups cannot. So here CLKA and CLKC can talk to each other but neither CLKA nor CLKC can communicate to CLKB or CLKD (or vice versa).

Note: It will take eight different set_false_path commands to accomplish the same thing that we can do using one set_clock_groups command